# GigaDevice Semiconductor Inc.

# GD30WS8805x PMIC for TWS Headset Charging Box

**Datasheet**

### **Table of Contents**

| Table      | of Contents                              | 2  |

|------------|------------------------------------------|----|

| List o     | of Figures                               | 4  |

| List o     | of Tables                                | 5  |

| 1 F        | eatures                                  | 6  |

| 2 A        | pplications                              | 6  |

| 3 G        | eneral description                       | 7  |

|            | evice overview                           |    |

| 4.1        | Device information                       | 8  |

| 4.2        | Block diagram                            |    |

| 4.3        | Pinout and pin assignment                |    |

| 4.4        | Pin definitions                          |    |

|            | unctional description                    |    |

| 5 F<br>5.1 | Operation modes                          |    |

| _          | ·                                        |    |

| 5.2        | Battery charging                         |    |

| _          | 2.2 Charge parameters                    |    |

| 5.3        | Synchronous boost converter              |    |

| 5.4        | Power path management                    |    |

|            | 4.1 Power path management                |    |

| 5.         | 4.2 LDO                                  | 14 |

| 5.5        | Earbud detection                         | 15 |

| 5.6        | NTC battery temperature                  | 15 |

| 5.7        | LED driver                               | 16 |

| 5.         | 7.1 LED connection and display mode      | 16 |

| 5.         | 7.2 LED Display Mode Configuration       | 18 |

| 5.         | 7.3 LED Driving Capability Configuration | 18 |

| 5.         | 7.4 LED Display Control by I2C           | 19 |

| 5.8        | Earbud communication                     | 19 |

| 5.9        | EN and IRQ                               | 20 |

| 5.10       | Over temperature protection              | 20 |

| 5.11       | l I2C interface                          | 20 |

| ;  | 5.12 | ? F         | Register Map                         | 21   |

|----|------|-------------|--------------------------------------|------|

|    | 5.   | 12.1        | Fault Register                       | . 21 |

|    | 5.   | 12.2        | Status Register 1                    | 23   |

|    | 5.   | 12.3        | Status Register 2                    |      |

|    |      | 12.4        | Control Register                     |      |

|    |      | 12.5        | User configure Register 1            |      |

|    |      | 12.6        | User configure Register 2            |      |

|    |      | 12.7        | User configure Register 3            |      |

|    |      | 12.8        | Watchdog Register                    |      |

|    |      | 12.9        | COML/R Register                      |      |

|    |      | 12.10       | LED Register                         |      |

|    |      | 12.11       | ADC Register                         |      |

|    |      | 12.12       | DEBUG Register                       |      |

| 6  | E    | lectri      | cal characteristics                  | 32   |

| (  | 6.1  | Ab          | solute maximum ratings               | 32   |

|    | 6.2  | Re          | commended operation conditions       | 32   |

|    |      |             |                                      |      |

| (  | 6.3  | Ele         | ectrical sensitivity                 | 33   |

| (  | 6.4  | Po          | wer supplies voltages and currents   | 33   |

| (  | 6.5  | Lo          | gic input characteristics            | 33   |

| (  | 6.6  | Ор          | en drain outputs characteristics     | 33   |

| (  | 6.7  | NT          | C characteristics                    | 34   |

| (  | 8.6  | Sw          | itching charger characteristics      | 34   |

| (  | 6.9  | Во          | ost converter characteristics        | 35   |

| (  | 6.10 | ) /         | ADC characteristics                  | 36   |

| (  | 6.11 | 1           | iming characteristics                | 37   |

| (  | 6.12 | ? E         | Earbud Output Switch characteristics | 37   |

| (  | 6.13 | <b>3</b> I: | 2C characteristics                   | 37   |

| (  | 6.14 | F           | Protection features                  | 38   |

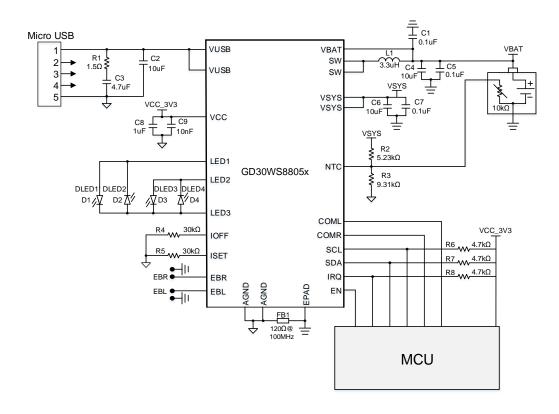

| 7  | Ty   | уріса       | l application circuit                | 40   |

| 8  | La   | ayou        | t guideline                          | 41   |

| 9  | P    | acka        | ge information                       | 42   |

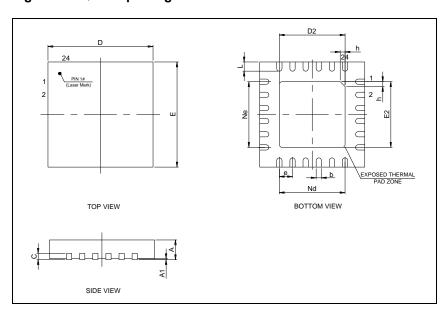

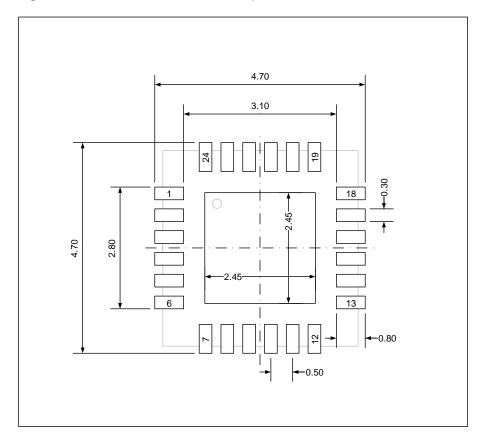

| ,  | 9.1  | QF          | N24 package information              | 42   |

| 9  | 9.2  | The         | ermal characteristics                | 44   |

| 10 | )    | Orde        | ering information                    | 45   |

| 11 |      | Revi        | sion history                         | 46   |

# **List of Figures**

| Figure 4-1 Block diagram for GD30WS8805x                    | 8  |

|-------------------------------------------------------------|----|

| Figure 4-2 GD30WS8805x QFN24 pinouts                        | 9  |

| Figure 5-1 Operation modes                                  | 11 |

| Figure 5-2 Battery charge state diagram                     | 12 |

| Figure 5-3 Battery charge cycle and charge parameters       | 13 |

| Figure 5-4 The principle diagram for LDO                    | 15 |

| Figure 5-5 Diagram for the NTC circuit                      | 15 |

| Figure 5-6 1-LED Mode                                       | 16 |

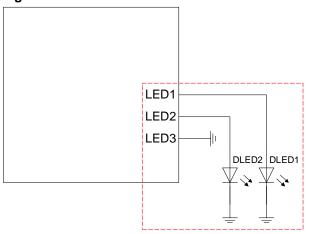

| Figure 5-7 2-LED Mode                                       | 16 |

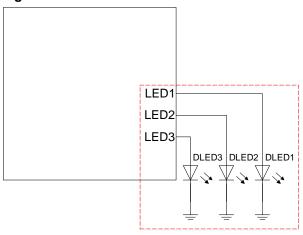

| Figure 5-8 3-LED Mode                                       | 17 |

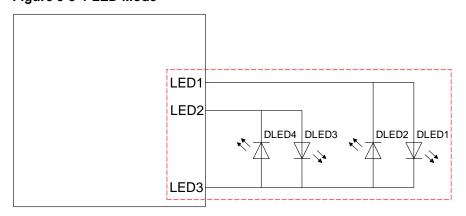

| Figure 5-9 4-LED Mode                                       | 17 |

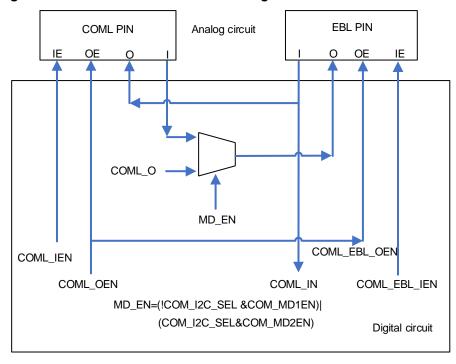

| Figure 5-10 The communication block diagram of COML and EBL | 19 |

| Figure 5-11 I2C communication flow                          | 21 |

| Figure 6-1 Constant current charging efficiency             | 34 |

| Figure 6-2 Constant current charging chip case temperature  | 35 |

| Figure 6-3 BOOST conversion efficiency                      | 36 |

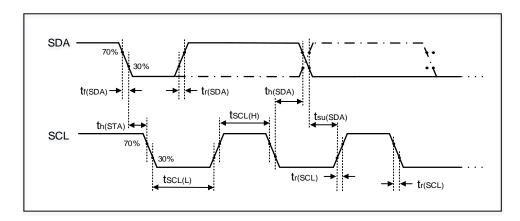

| Figure 6-4 I2C bus timing diagram                           | 37 |

| Figure 7-1 Typical GD30WS8805x application circuit          | 40 |

| Figure 8-1 Typical GD30WS8805x layout guideline             | 41 |

| Figure 9-1 QFN24 package outline                            | 42 |

| Figure 9-2 QFN24 recommended footprint                      | 43 |

### **List of Tables**

| Table 4-1 Device information for GD30WS8805x             | 8    |

|----------------------------------------------------------|------|

| Table 4-2 GD30WS8805x QFN24 pin definitions              | 9    |

| Table 5-1 Description of resistors for the NTC circuit   | . 15 |

| Table 5-2 1-LED Display Mode                             | . 16 |

| Table 5-3 2-LED Display Mode                             | . 17 |

| Table 5-4 3-LED Display Mode                             | . 17 |

| Table 5-5 4-LED Display Mode                             | . 18 |

| Table 5-6 LED Display Mode Register                      | . 18 |

| Table 5-7 LED Driving Register                           | . 18 |

| Table 5-8 LED Control Register                           | . 19 |

| Table 6-1 Absolute maximum ratings                       | . 32 |

| Table 6-2 Recommended operation conditions               | . 32 |

| Table 6-3 Electrostatic Discharge characteristics        | . 33 |

| Table 6-4 Power supplies voltages and currents           | . 33 |

| Table 6-5 Logic input characteristics                    | . 33 |

| Table 6-6 Open drain output characteristics              | . 33 |

| Table 6-7 NTC characteristics                            | . 34 |

| Table 6-8 Charger characteristics                        | . 34 |

| Table 6-9 Boost converter characteristics                | . 35 |

| Table 6-10 ADC characteristics                           | . 36 |

| Table 6-11 Timing characteristics                        | . 37 |

| Table 6-12 Earbud output switch characteristics          | . 37 |

| Table 6-13 I2C characteristics                           | . 37 |

| Table 6-14 Protection features characteristics           | . 38 |

| Table 9-1 QFN24 dimensions                               |      |

| Table 9-2 Package thermal characteristics <sup>(1)</sup> | . 44 |

| Table 10-1 Part ordering code for GD30WS8805x devices    | . 45 |

| Table 11-1 Revision history                              | 46   |

#### 1 Features

- Extreme low quiescent current, <5µA in sleep mode

- Charging features

- Switching charging up to 1.2A maximum current programmable through ISET

- Support variety of battery chemistries, 4.1/4.2/4.3/4.35/4.4V @0.5%

- Full charge cycle: pre-charge, constant current and constant voltage

- Charging current and pre-charging current are all programmable through I2C

#### ■ Boost converter

- Support up to 600mA load current

- High efficiency synchronous boost converter @95%

- Output current limit programmable through I2C, 1.6A/1.8A/2.0A/2.2A

#### ■ Power path management

- Power path management allows simultaneous battery charging and system supply,

system discharge priority

- When the system load increases, the charging current is reduced dynamically according to the input current and system voltage

- USB current limit programmable through I2C, 95%/100%/105%/110% @IcccH + 0.5A (Maximum current 3A)

- Over voltage protection up to 5.6V, V<sub>SYS</sub> voltage regulation limit: 4.6V

#### Protection features

- Short Circuit Protection

- Over/Under temperature protection

- Input Over Voltage/Current Protection

- Boost over voltage (OV) during charge @5.5V

- Boost under voltage (UV) when charge/discharge @4.3V

#### Additional features

- 3.3V LDO support 50mA

- Programmable LED driver

- Low external component count

- Simple I<sup>2</sup>C compatible interface

### 2 Applications

- TWS earbuds charging case

- Headsets and hearing aids

- Low battery applications such as smart watches and fitness accessories

- Patient monitors and portable medical equipment

### 3 General description

The GD30WS8805x is a highly integrated, programmable, low quiescent current power management integrated circuit (PMIC) that integrates the most common needs for wearables and low power battery applications.

The GD30WS8805x integrates a switching charger of programmable charging current (up to 1.2A) and a synchronous boost converter at fixed 5V output. The IC also includes a 12-bit ADC for battery gauge monitoring, and a low quiescent current, low noise LDO capable of delivering 50mA load current.

The device integrates advanced power path management and control that allow the device to provide power to the system while charging the battery even with poor adapters. The dynamic power path management automatically balances the currents delivered to the system and battery charging. A high voltage and over current protection circuit is implemented in the IC to protect it from high input voltage as high as 20V.

The GD30WS8805x device supports charge current up to 1.2A and termination current down to 5mA. The maximum charge current is set at a default of 1.2A and is programmable by connecting an external resistor from ISET pin to ground. The battery is charged using a standard Li-lon charge profile with three phases: pre-charge, constant current and constant voltage regulation.

The device has several power saving modes to increase battery life whether the product is in storage or in operation. The quiescent current could be as low as 5uA when it is in sleep mode and thus most battery could sustain more than a year in shelf.

The versatile features of GD30WS8805x allow for it to best used in wearable applications such as headsets, earbuds and hearing aids, or low battery applications such as smart watches and fitness accessories, or patient monitors and portable medical equipment.

#### 4 Device overview

#### 4.1 Device information

Table 4-1 Device information for GD30WS8805x

| Part Number | Package    | Function    | Description                  |

|-------------|------------|-------------|------------------------------|

| GD30WS8805x | QFN24(4X4) | MCU version | Cooperate with MCU solution, |

| GD30W36603X | QFN24(4A4) | MCO version | supports EN enable control   |

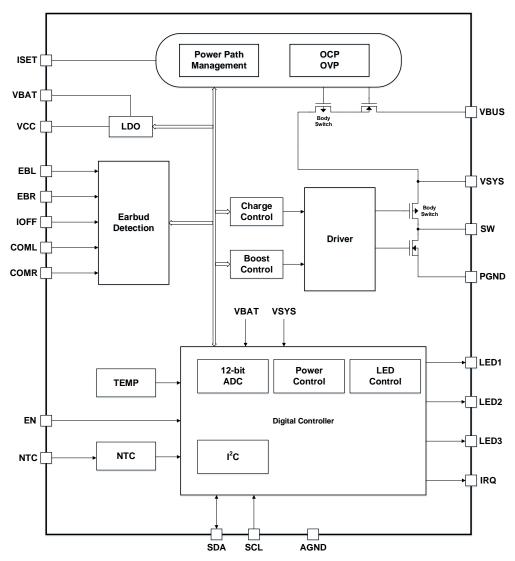

### 4.2 Block diagram

Figure 4-1 Block diagram for GD30WS8805x

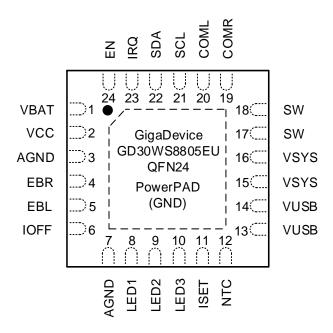

### 4.3 Pinout and pin assignment

Figure 4-2 GD30WS8805x QFN24 pinouts

#### 4.4 Pin definitions

Table 4-2 GD30WS8805x QFN24 pin definitions

| Pin Name | Pins  | Pin Type | Functions description                                                    |  |  |

|----------|-------|----------|--------------------------------------------------------------------------|--|--|

| VBAT     | 1     | Р        | Connect to positive node of a battery.                                   |  |  |

| VCC      | 2     | Р        | LDO output voltage, connect a capacitor to ground.                       |  |  |

| AGND     | 3     | G        | Ground.                                                                  |  |  |

| EBR      | 4     | I/O      | Positive terminal for right earbud.                                      |  |  |

| EBL      | 5     | I/O      | Positive terminal for left earbud.                                       |  |  |

| IOFF     | 6     | I        | Set the termination current for BOOST.                                   |  |  |

| AGND     | 7     | G        | Ground.                                                                  |  |  |

| LED1     | 8     | 0        | LED driver #1 for battery gauge monitor or other.                        |  |  |

| LED2     | 9     | 0        | LED driver #2 for battery gauge monitor or other.                        |  |  |

| LED3     | 10    | 0        | LED driver #3 for battery gauge monitor or other.                        |  |  |

| ISET     | 11    | I        | Set the charge current by connecting a resistor to ground.               |  |  |

| NTC      | 12    | I        | Thermistor terminal voltage for battery, or pull high to DISABLE the IC. |  |  |

| VUSB     | 13,14 | Р        | ower input from USB or 5-V voltage source.                               |  |  |

| VSYS | 15,16 | Р   | Output of boost converter or system voltage.       |  |

|------|-------|-----|----------------------------------------------------|--|

| SW   | 17,18 | Р   | Switching node, connecting to VBAT by an inductor. |  |

| COMR | 19    | I/O | Right earbud communication input and output.       |  |

| COML | 20    | I/O | Left earbud communication input and output.        |  |

| SCL  | 21    | ı   | I2C communication to the host controller, clock.   |  |

| SDA  | 22    | I/O | I2C communication to the host controller, data.    |  |

| IRQ  | 23    | 0   | Interrupt output.                                  |  |

| EN   | 24    | I   | IC enable.                                         |  |

| PGND | EPAD  | G   | Device power ground.                               |  |

#### Notes:

1. Type: I = input, O = output, I/O = input or output, P = power, G = Ground.

### 5 Functional description

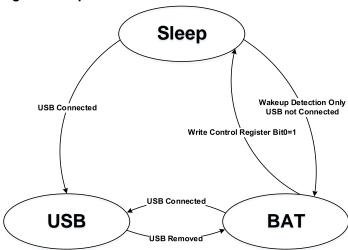

#### 5.1 Operation modes

The GD30WS8805x IC has three different operation modes: Sleep, Battery and USB operation mode, as shown in Figure 5-1.

Figure 5-1 Operation modes

#### 5.2 Battery charging

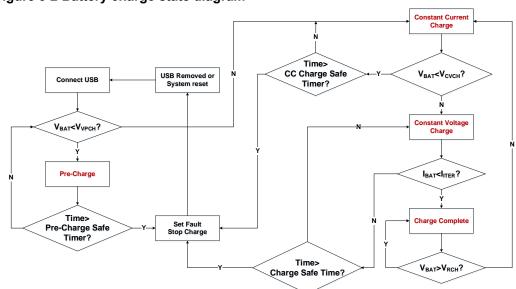

#### **5.2.1** Battery charger state

The GD30WS8805x device integrates a switching charger that allows the battery to be charged with a programmable charge current up to 1.2A. In addition to the charge current, other charging parameters can be also programmed through I2C such as the battery regulation voltage, pre-charge current. The device supports multiple battery regulation voltage regulation settings ( $V_{\text{CVCH}}$ ) and charge current ( $I_{\text{CCCH}}$ ) options to support multiple battery chemistries for single-cell applications. A full one-cell charger state diagram as shown in Figure 5-2 is implemented in the IC.

Figure 5-2 Battery charge state diagram

#### 5.2.2 Charge parameters

The maximum charge current is programmed by a resistor connected from the ISET pin to ground. The earbud light load current is programmed by a resistor connected from the IOFF pin to ground. The resistor value can be calculated as:

$$R_{CCCH} = \frac{10}{I_{CCCH}} k\Omega$$

$$I_{PCH} = \frac{I_{CCCH}}{10}$$

$$R_{IOFF} = \frac{500}{I_{IOFF}} k\Omega$$

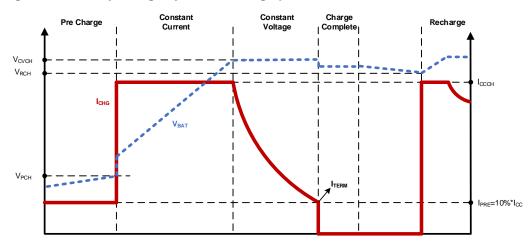

Where the unit of  $I_{CCCH}$  is A, the unit of  $I_{IOFF}$  is mA. The charge current also varies in different charging stages constant current loop (CC), constant voltage loop (CV). During the charging process, all control loops are enabled and the one that is dominant takes control regulating the charge current as needed. The relevant charge parameters and control loops are defined as in Figure 5-3.

Figure 5-3 Battery charge cycle and charge parameters

The charger input has back to back blocking FETs to prevent reverse current flow from VBAT to VUSB. They also integrate control circuitry regulating the input current and prevents excessive currents from being drawn from the USB power supply for more reliable operation.

#### 5.3 Synchronous boost converter

The integrated synchronous boost converter is a wide input range, high-efficiency, DC-to-DC step-up switching regulator. It is capable of delivering up to 3W of output power, integrated with a  $150\,\mathrm{m}\Omega$  high side PMOS and a  $150\,\mathrm{m}\Omega$  low side NMOS. It uses a PWM current-mode control scheme. An error amplifier integrates error between the internal feedback signal proportional to VSYS and the internal reference voltage. The output of the integrator is then compared to the sum of a current-sense signal and the slope compensation ramp. This operation generates a PWM signal that modulates the duty cycle of the power MOSFETs to achieve regulation for output voltage.

Integrated VBAT to VSYS synchronous boost output function, the output voltage is 5V, which can be set to  $4.8V \sim 5.15V$  by I2C. The boost module integrates the current limiting function. When the load current is too large, the chip enters the cycle-by-cycle current limiting mode, limiting the peak inductor current to 2.0A, which can be configured to 1.6A/1.8A/2.0A/2.2A by I2C. At the same time, the output voltage starts to drop. When the output voltage drops to 4.3V, the short-circuit protection is triggered.

The boost module also integrates an overvoltage protection function. When the output voltage is higher than 5.5V, the overvoltage protection is triggered. When the voltage of the boost module drops below 2.8V during the working process of the booster module, the boost module is automatically closed and locked in the under voltage lockout state.

The boost regulator provides excellent stability over a wide range of output current and operates in DCM at light loads for excellent efficiency. The switching frequency is fixed at 1MHz to reduce the external inductor size. The boost regulator is disabled when USB voltage is detected to save power.

#### 5.4 Power path management

#### **5.4.1** Power path management

The device integrates advanced power path management and control that allows the device to provide power to the system while charging the battery even with low power adapters. The dynamic power path management is able to automatically balance the currents delivered to the system and battery charging.

The charging current can be set to  $I_{CCCH}$  through the off-chip resistor connected to the ISET pin, and the chip input current is limited to  $I_{CCCH}$  +0.5A by the input current limit switch. In the charging and discharging mode, the system discharge priority. There are two situations that will cause the charging current to drop.

- When the discharge current plus the rated charging is higher than I<sub>CCCH</sub> +0.5A, the dynamic path management loop automatically reduces the charging current to meet the discharge demand.

- 2) When the power supply capacity of the input adapter is lower than Iccch+0.5A, and the rated charging current plus the VSYS discharge current is greater than the power supply capacity of the adapter, the VSYS voltage will drop, as the VSYS voltage drops to 4.6V, the charging current will be reduced through the feedback loop.

The chip also integrates the charging current temperature modulation function, when the chip temperature exceeds 110 degrees Celsius, the charging current is automatically reduced.

The input current limit switch also integrates short-circuit protection and over-current protection. When the current in the input switch exceeds 3A, the over-current protection is triggered. When the VSYS voltage drops below 4V, the short-circuit protection is triggered, the system stops working, and the input switch is closed. The chip enters hiccup mode and restarts every 250ms to check whether the abnormality exists. If the abnormality is removed, the chip returns to normal operation

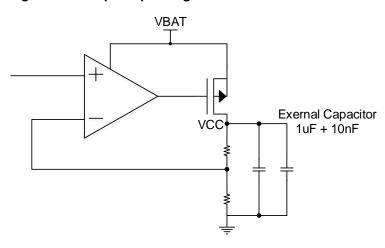

#### 5.4.2 LDO

A linear regulator is integrated to supply part of the chip and external circuits or MCU.

Output voltage of the LDO is 3.3V and the output driving current is 50mA. When output current exceeds 50mA, the output value will drop. When the chip works in sleep mode, LDO will enter low power mode to save power, which provides 10mA driving capability.

Figure 5-4 The principle diagram for LDO

#### 5.5 Earbud detection

The circuit detects the output current from EBL/EBR to show that earbud is inserted. EBL and EBR are independent channels which detect earbuds individually.

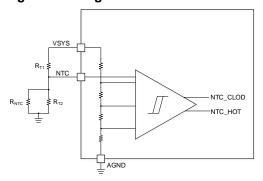

#### 5.6 NTC battery temperature

The GD30WS8805x chip integrates an NTC battery temperature protection circuit, which provides the over-temperature protection of high temperature 55°C and low temperature -10°C. The corresponding high and low temperature threshold voltages are respectively 30% and 60% of the input system voltage. When the battery temperature exceeds 55°C or fall below -10°C, the correlative high or low temperature output will be set high separately. If NTC pin is pulled down to GND, the NTC function is closed.

Figure 5-5 Diagram for the NTC circuit

Table 5-1 Description of resistors for the NTC circuit

| Symbol           | Parameter                     | Typical value | Unit |

|------------------|-------------------------------|---------------|------|

| R <sub>NTC</sub> | NTC thermistor                | 10            | ΚΩ   |

| R <sub>T1</sub>  | Resistor for voltage division | 5.23          | ΚΩ   |

| R <sub>T2</sub>  | Resistor for voltage division | 9.31          | ΚΩ   |

#### 5.7 LED driver

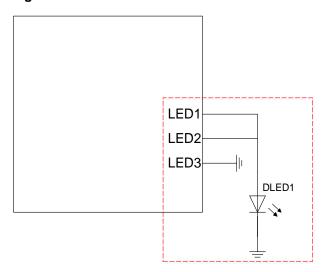

The chip supports 1-4 LED mode (see Table 5-2 to Table 5-5). The GD30WS8805x supports LED control by I2C (see Table 5-6 to Table 5-8).

### 5.7.1 LED connection and display mode

Figure 5-6 1-LED Mode

Table 5-2 1-LED Display Mode

| Mode           | Battery Status | DLED1               |  |  |  |

|----------------|----------------|---------------------|--|--|--|

| Charge         | Full           | Always On           |  |  |  |

| Charge         | Charging       | Blink at 1Hz        |  |  |  |

| Disabanna      | Normal Power   | On for 8s           |  |  |  |

| Discharge      | Low Battery    | Blink at 1Hz for 8s |  |  |  |

| Earbud plug in | _              | Blink at 1Hz for 1s |  |  |  |

Figure 5-7 2-LED Mode

**Table 5-3 2-LED Display Mode**

| Mode           | Battery Status | DLED1               | DLED2        |

|----------------|----------------|---------------------|--------------|

| Chargo         | Full           | Off                 | Always On    |

| Charge         | Charging       | Off                 | Blink at 1Hz |

| Discharge      | Normal Power   | On for 8s           | Off          |

| Discharge      | Low Battery    | Blink at 1Hz for 8s | Off          |

| Earbud plug in | _              | Blink at 1Hz for 1s |              |

Figure 5-8 3-LED Mode

Table 5-4 3-LED Display Mode

| Mode           | Battery Level | DLED1               | DLED2        | DLED3        |

|----------------|---------------|---------------------|--------------|--------------|

|                | Full          | Always On           | Always On    | Always On    |

| Charge         | 66%-100%      | Always On           | Always On    | Blink at 1Hz |

| Charge         | 33%-66%       | Always On           | Blink at 1Hz | Off          |

|                | 0%-33%        | Blink at 1Hz        | Off          | Off          |

|                | 66%-100%      | On for 8s           | On for 8s    | On for 8s    |

| Discharge      | 33%-66%       | On for 8s           | On for 8s    | Off          |

| Discharge      | 5%-33%        | On for 8s           | Off          | Off          |

|                | 0%-5%         | Blink at 1Hz for 8s | Off          | Off          |

| Earbud plug in |               | Blink at 1Hz for 1s |              |              |

Figure 5-9 4-LED Mode

Table 5-5 4-LED Display Mode

| Mode           | Battery<br>Level | DLED1                  | DLED2        | DLED3        | DLED4        |

|----------------|------------------|------------------------|--------------|--------------|--------------|

|                | Full             | Always On              | Always On    | Always On    | Always On    |

|                | 75%-100%         | Always On              | Always On    | Always On    | Blink at 1Hz |

| Charge         | 50%-75%          | Always On              | Always On    | Blink at 1Hz | Off          |

|                | 25%-50%          | Always On              | Blink at 1Hz | Off          | Off          |

|                | 0%-25%           | Blink at 1Hz           | Off          | Off          | Off          |

|                | 75%-100%         | On for 8s              | On for 8s    | On for 8s    | On for 8s    |

|                | 50%-75%          | On for 8s              | On for 8s    | On for 8s    | Off          |

| Discharge      | 25%-50%          | On for 8s              | On for 8s    | Off          | Off          |

| Discharge      | 5%-25%           | On for 8s              | Off          | Off          | Off          |

|                | 0%-5%            | Blink at 1Hz<br>for 8s | Off          | Off          | Off          |

| Earbud plug in | _                | Blink at 1Hz for 1s    |              |              |              |

### **5.7.2 LED Display Mode Configuration**

**Table 5-6 LED Display Mode Register**

| Register<br>Address | Bits  | R/W             | Fields         | Description                     |

|---------------------|-------|-----------------|----------------|---------------------------------|

|                     |       |                 |                | LED mode status, default: 2'b00 |

|                     |       |                 |                | 00: 2 LED Mode                  |

| 0x0d                | [2:1] | RW LED_I2C_MDST | 01: 3 LED Mode |                                 |

|                     | 10: 1 |                 |                | 10: 1 LED Mode                  |

|                     |       |                 |                | 11: 4 LED Mode                  |

### **5.7.3** LED Driving Capability Configuration

**Table 5-7 LED Driving Register**

| Register<br>Address | Bits  | R/W | Fields  | Description                                   |

|---------------------|-------|-----|---------|-----------------------------------------------|

|                     |       |     |         | LED current set, default: 2'b10<br>00: 0.5 mA |

| 0x04                | [5:4] | RW  | LED_DRV | 01: 1 mA<br>10: 2 mA                          |

|                     |       |     |         | 11: 4 mA                                      |

#### 5.7.4 LED Display Control by I2C

**Table 5-8 LED Control Register**

| Register<br>Address | Bits                  | R/W | Fields                            | Description                       |

|---------------------|-----------------------|-----|-----------------------------------|-----------------------------------|

|                     |                       |     |                                   | I2C control enable, default: 1'b0 |

| 0x0d                | [0]                   | RW  | LED_I2C_EN                        | 0: LED hardware control           |

|                     |                       |     |                                   | 1: LED I2C control                |

|                     |                       |     |                                   | LED Status, default: 4'b0000      |

|                     | 0x0d [13:10] RW LED_I |     | [13]: LED4 Status (0: Off, 1: On) |                                   |

| 0x0d                |                       | RW  | LED_I2C_ST                        | [12]: LED3 Status (0: Off, 1: On) |

|                     |                       |     |                                   | [11]: LED2 Status (0: Off, 1: On) |

|                     |                       |     |                                   | [10]: LED1 Status (0: Off, 1: On) |

#### 5.8 Earbud communication

MCU supports up to 2M bidirectional communication with earbud by COML/R pin and EBL/R pin. There are two kinds of Earbud communication. One is through changing and reading COML/R pin level for communication, configure COM\_I2C\_SEL to 0 & COM\_MD1EN to 1. The other is to communicate through the I2C control register changes, configure COM\_I2C\_SEL to 1 & COM\_MD2EN to 1. The communication block diagram of COML and EBL is shown in Figure 5-10.

Figure 5-10 The communication block diagram of COML and EBL

When EBL/R is used as the output pin, the output low voltage is 0V, and the output high

voltage is VBAT or 5V. (When boost is used, the output high voltage is 5V, otherwise the output high voltage is VBAT)

When COML/R is used as the output pin, the output low voltage is 0V, and the output high voltage is VBAT.

When EBL/R or COML/R is used as the input pins, the input low voltage is 0V - 0.35 \* VCC, and the input high voltage is 0.65 \* VCC - 5.5V. The input characteristics follow Table 6-5.

#### 5.9 EN and IRQ

The IRQ pin will generate an 8ms neg-edge pulse, when fault or work status are appeared. MCU can wake up the chip by giving a high voltage on EN pin.

IRQ sources include the following:

- 1) Battery charge end

- 2) Watch dog time out fault

- 3) Battery charge time out fault

- 4) Battery pre-charge time out fault

- 5) Over temperature fault (more than 150°C)

- 6) NTC Hot fault

- 7) NTC cold fault

- 8) VSYS under voltage fault

- 9) VSYS over voltage fault

- 10) USB plug in

- 11) USB pull out

- 12) Left or right earbud plug in

- 13) Left or right earbud pull out

- 14) Left or right earbud light load

- 15) Left or right earbud short/under voltage fault

- 16) VUSB over voltage fault

- 17) VBAT over voltage fault when charge the battery

- 18) VBAT under voltage fault when the battery discharge

#### 5.10 Over temperature protection

If the die temperature exceeds the trip point of the thermal shutdown limit  $(T_{SD})$ , all the circuits are disabled, and the IRQ pin is pulled low.

#### 5.11 I2C interface

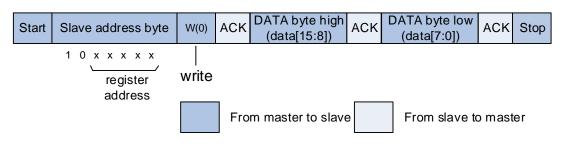

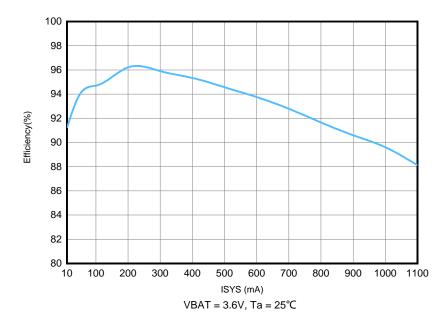

The I2C (inter-integrated circuit) module provides an I2C interface which is an industry standard two-line serial interface for MCU to communicate with external I2C interface. I2C bus uses two serial lines: a serial data line (SDA), and a serial clock line (SCL).

The I2C interface implements standard I2C protocol with standard-mode (up to 100 kHz) and fast-mode (up to 400 kHz). The I2C interface only supports Slave-mode. The I2C interface receive data on rising SCL and transmit data on falling SCL.

Figure 5-11 I2C communication flow

The data format is fixed:

8bit function (2'b10 + 5bit(register address), +1bit(1'b0-write, 1'b1-read))

- + 8bit data[15:8]

- + 8bit data[7:0].

### 5.12 Register Map

#### 5.12.1 Fault Register

Address: 0b 00000

| Bits | R/W   | fields          | default | Description                                             |

|------|-------|-----------------|---------|---------------------------------------------------------|

|      |       |                 |         | I2C fault                                               |

| 45   | D) 4/ | 100 401/ 541117 |         | Software can clear it by writing 1.                     |

| 15   | RW    | I2C_ACK_FAULT   | 0b0     | 0: I2C normally                                         |

|      |       |                 |         | 1: I2C ACK fault/clear                                  |

| 14   | R     | Reserved        | 0b0     | Must be kept at reset value.                            |

|      |       |                 | 0b0     | Pre-charge timeout fault                                |

|      |       |                 |         | Software can clear it by writing Control Register bit10 |

| 13   | R     | PCH_TO_FAULT    |         | I2C_CLR_FAULT.                                          |

|      |       |                 |         | 0: Pre-charge normally                                  |

|      |       |                 |         | 1: Pre-charge timeout fault                             |

| 10   | -     | CH TO FAULT     |         | Charge timeout fault                                    |

| 12   | R     | CH_TO_FAULT     | 0b0     | Software can clear it by writing Control Register bit10 |

| Bits | R/W  | fields            | default | Description                                             |

|------|------|-------------------|---------|---------------------------------------------------------|

|      | 1211 | 110100            |         | I2C CLR FAULT.                                          |

|      |      |                   |         | 0: Charge normally                                      |

|      |      |                   |         | 1: Charge timeout fault                                 |

|      |      |                   |         | Watchdog timeout fault                                  |

|      |      |                   |         | Software can clear it by writing Control Register bit13 |

|      |      |                   |         | WDG_CLR or writing Watchdog Register bits               |

| 11   | R    | WDG_FAULT         | 0b0     | WDG_DATA[9:1].                                          |

|      |      |                   |         | 0: Watchdog normally                                    |

|      |      |                   |         |                                                         |

|      |      |                   |         | 1: Watchdog timeout fault                               |

| 40   | _    | VILLED OC FALILIT | 050     | VUSB over current fault                                 |

| 10   | R    | VUSB_OC_FAULT     | 0b0     | 0: VUSB current normally                                |

|      |      |                   |         | 1: VUSB over current fault                              |

|      |      |                   |         | VUSB over voltage fault                                 |

| 9    | R    | VUSB_OV_FAULT     | 0b0     | 0: VUSB voltage normally                                |

|      |      |                   |         | 1: VUSB over voltage fault                              |

|      |      |                   |         | EBR under voltage fault                                 |

|      |      |                   |         | Software can clear it by writing Control Register bit10 |

| 8    | R    | EBR_UV_FAULT      | 0b0     | I2C_CLR_FAULT.                                          |

|      |      |                   |         | 0: EBR voltage normally                                 |

|      |      |                   |         | 1: EBR under voltage fault                              |

|      |      |                   |         | EBL under voltage fault                                 |

|      |      |                   |         | Software can clear it by writing Control Register bit10 |

| 7    | R    | EBL_UV_FAULT      | 0b0     | I2C_CLR_FAULT.                                          |

|      |      |                   |         | 0: EBL voltage normally                                 |

|      |      |                   |         | 1: EBL under voltage fault                              |

|      |      |                   |         | VSYS over voltage fault                                 |

|      |      |                   |         | Software can clear it by writing Control Register bit10 |

| 6    | R    | VSYS_OV_FAULT     | 0b0     | I2C_CLR_FAULT.                                          |

|      |      |                   |         | 0: VSYS voltage normally                                |

|      |      |                   |         | 1: VSYS over voltage fault                              |

|      |      |                   |         | VSYS under voltage fault                                |

|      |      |                   |         | Software can clear it by writing Control Register bit10 |

| 5    | R    | VSYS_UV_FAULT     | 0b0     | I2C_CLR_FAULT.                                          |

|      |      |                   |         | 0: VSYS voltage normally                                |

|      |      |                   |         | 1: VSYS under voltage fault                             |

|      |      |                   |         | NTC_HOT fault                                           |

|      |      |                   |         | Software can clear it by writing Control Register bit10 |

| 4    | R    | NTC_HOT_FAULT     | 0b0     | I2C_CLR_FAULT.                                          |

|      | • •  |                   |         | 0: NTC normally                                         |

|      |      |                   |         | 1: NTC hot fault                                        |

|      |      |                   |         | NTC_COLD fault                                          |

| 3    | R    | NTC_COLD_FAULT    | 0b0     | Software can clear it by writing Control Register bit10 |

|      | l    |                   |         | ,                                                       |

| Bits | R/W | fields        | default | Description                                             |

|------|-----|---------------|---------|---------------------------------------------------------|

|      |     |               |         | I2C_CLR_FAULT.                                          |

|      |     |               |         | 0: NTC normally                                         |

|      |     |               |         | 1: NTC cold fault                                       |

|      |     |               |         | VBAT over voltage fault                                 |

|      |     |               |         | Software can clear it by writing Control Register bit10 |

| 2    | R   | VBAT_OV_FAULT | 0b0     | I2C_CLR_FAULT.                                          |

|      |     |               |         | 0: VBAT voltage normally                                |

|      |     |               |         | 1: VBAT over voltage fault                              |

|      |     |               |         | VBAT under voltage fault                                |

|      |     |               |         | Software can clear it by writing Control Register bit10 |

| 1    | R   | VBAT_UV_FAULT | 0b0     | I2C_CLR_FAULT.                                          |

|      |     |               |         | 0: VBAT voltage normally                                |

|      |     |               |         | 1: VBAT under voltage fault                             |

|      |     |               |         | Over temperature fault                                  |

| 0    | R   | TEMP_FAULT    | 0b0     | 0: The battery temperature normally                     |

|      |     |               |         | 1: The battery over temperature fault                   |

### 5.12.2 Status Register 1

Address: 0b 00001

| Bits | R/W | fields      | default | Description                                              |

|------|-----|-------------|---------|----------------------------------------------------------|

|      |     |             |         | Pre-charge enable flag                                   |

| 15   | R   | PCH_ENF     | 0b0     | 0: Pre-charge is disabled                                |

|      |     |             |         | 1: Pre-charge is enabled                                 |

|      |     |             |         | VUSB enable flag                                         |

| 14   | R   | VUSB_ENF    | 0b0     | 0: VUSB is disabled                                      |

|      |     |             |         | 1: VUSB is enabled                                       |

|      |     |             |         | VUSB over voltage detection enable flag                  |

| 13   | R   | VUSBOV_ENF  | 0b0     | 0: VUSB over voltage detection is disabled               |

|      |     |             |         | 1: VUSB over voltage detection is enabled                |

|      |     |             |         | VBAT pre-charge output flag                              |

| 12   | R   | VBAT_PCH_OF | 0b0     | 0: VBAT is higher than pre-charge threshold voltage VPCH |

|      |     |             |         | 1: VBAT is lower than pre-charge threshold voltage VPCH  |

|      |     |             |         | VBAT re-charge output flag                               |

| 11   | R   | VBAT_RCH_OF | 0b0     | 0: VBAT is higher than re-charge threshold voltage VRCH  |

|      |     |             |         | 1: VBAT is lower than re-charge threshold voltage VRCH   |

|      |     |             |         | EBL enable flag                                          |

| 10   | R   | EBL_ENF     | 0b0     | 0: EBL is closed                                         |

|      |     |             |         | 1: EBL is opened                                         |

| 0    |     | EDD ENE     |         | EBR enable flag                                          |

| 9    | R   | EBR_ENF     | 0b0     | 0: EBR is closed                                         |

| Bits | R/W | fields    | default | Description                             |

|------|-----|-----------|---------|-----------------------------------------|

|      |     |           |         | 1: EBR is opened                        |

| 8    | R   | Reserved  | 0b0     | Must be kept at reset value.            |

|      |     |           |         | USB plug in flag                        |

| 7    | R   | USB_PLINF | 0b0     | 0: USB is not plugged in                |

|      |     |           |         | 1: USB is plugged in                    |

|      |     |           |         | Charge end flag                         |

| 6    | R   | CH_ENDF   | 0b0     | 0: Charge is not ended                  |

|      |     |           |         | 1: Charge is ended                      |

|      |     |           |         | Constant current charge end flag        |

| 5    | R   | CCCH_ENDF | 0b0     | 0: Constant current charge is not ended |

|      |     |           |         | 1: Constant current charge is ended     |

|      |     |           |         | Left earbud plug in flag                |

| 4    | R   | EBL_PLINF | 0b0     | 0: Left earbud is not plugged in        |

|      |     |           |         | 1: Left earbud is plugged in            |

|      |     |           |         | Right earbud plug in flag               |

| 3    | R   | EBR_PLINF | 0b0     | 0: Right earbud is not plugged in       |

|      |     |           |         | 1: Right earbud is plugged in           |

|      |     |           |         | Left earbud current load flag           |

| 2    | R   | EBL_IOFFF | 0b0     | 0: Heavy load                           |

|      |     |           |         | 1: Light load                           |

|      |     |           |         | Right earbud current load flag          |

| 1    | R   | EBR_IOFFF | 0b0     | 0: Heavy load                           |

|      |     |           |         | 1: Light load                           |

|      | -   |           |         | Boost enable flag                       |

| 0    | R   | BST_ENF   | 0b0     | 0: Boost is disabled                    |

|      |     |           |         | 1: Boost is enabled                     |

### 5.12.3 Status Register 2

Address: 0b 00010

| Bits | R/W | fields      | default | Description                                |

|------|-----|-------------|---------|--------------------------------------------|

| 15:8 | R   | Reserved    | 0b0     | Must be kept at reset value.               |

|      |     |             |         | EBL under voltage detection enable flag    |

| 7    | R   | EBL_UVENF   | 0b0     | 0: EBL under voltage detection is disabled |

|      |     |             |         | 1: EBL under voltage detection is enabled  |

|      |     |             |         | EBR under voltage detection enable flag    |

| 6    | R   | EBR_UVENF   | 0b0     | 0: EBR under voltage detection is disabled |

|      |     |             |         | 1: EBR under voltage detection is enabled  |

|      |     |             |         | Re-charge comparator enable flag           |

| 5    | R   | RCHCMP_ENF  | 0b0     | 0: Re-charge comparator is disabled        |

|      |     |             |         | 1: Re-charge comparator is enabled         |

| 4    | R   | VBAT_OV_ENF | 0b0     | VBAT over voltage detection enable flag    |

| Bits | R/W | fields     | default | Description                                |

|------|-----|------------|---------|--------------------------------------------|

|      |     |            |         | 0: VBAT over voltage detection is disabled |

|      |     |            |         | 1: VBAT over voltage detection is enabled  |

| 3:2  | R   | Reserved   | 0b0     | Must be kept at reset value.               |

|      |     |            |         | Pre- charge comparator enable flag         |

| 1    | R   | PCHCMP_ENF | 0b0     | 0: Pre-charge comparator is disabled       |

|      |     |            |         | 1: Pre-charge comparator is enabled        |

|      |     |            |         | Charge enable flag                         |

| 0    | R   | CH_ENF     | 0b0     | 0: Charge is disabled                      |

|      |     |            |         | 1: Charge is enabled                       |

### **5.12.4** Control Register

Address: 0b 00011

| Bits | R/W | fields        | default | Description                                              |

|------|-----|---------------|---------|----------------------------------------------------------|

| 15   | RW  | Reserved      | 0b0     | Must be kept at reset value.                             |

|      |     |               |         | Temperature regulation enable                            |

| 14   | RW  | TEMPREG_EN    | 0b0     | 0: Enable temperature regulation                         |

|      |     |               |         | 1: Disable temperature regulation                        |

|      |     |               |         | Feed watchdog                                            |

|      |     |               |         | Software can clear it by writing 1 to this bit, or reset |

| 13   | RW  | WDG_CLR       | 0b0     | watchdog register bits WDG_DATA[9:1].                    |

|      |     |               |         | 0: Watchdog normally                                     |

|      |     |               |         | 1: Feed watchdog                                         |

| 12   | R   | Reserved      | 0b0     | Must be kept at reset value.                             |

|      |     |               |         | ADC enable                                               |

| 11   | RW  | ADC_EN        | 0b0     | 0: Disable ADC                                           |

|      |     |               |         | 1: Enable ADC                                            |

|      |     |               |         | I2C clear all faults                                     |

| 10   | RW  | I2C_CLR_FAULT | 0b0     | 0: No effect                                             |

|      |     |               |         | 1: Clear all faults                                      |

|      |     |               |         | Reset all chip                                           |

| 9    | RW  | RST_ALL       | 0b0     | 0: No effect                                             |

|      |     |               |         | 1: Reset all chip                                        |

|      |     |               |         | Reset all chip but I2C itself                            |

| 8    | RW  | RST_OTHS      | 0b0     | 0: No effect                                             |

|      |     |               |         | 1: Reset all chip but I2C itself                         |

|      |     |               |         | ADC clock selection                                      |

|      |     |               |         | 00: ADC clock is 2MHz                                    |

| 7:6  | RW  | ADC_CLKSEL    | 0b0     | 01: ADC clock is 1MHz                                    |

|      |     |               |         | 10: ADC clock is 500kHz                                  |

|      |     |               |         | 11: ADC clock is 250kHz                                  |

| 5    | R   | Reserved      | 0b0     | Must be kept at reset value.                             |

| Bits | R/W | fields | default | Description           |

|------|-----|--------|---------|-----------------------|

|      |     |        |         | Boost enable          |

| 4    | RW  | BST_EN | 0b0     | 0: Disable boost      |

|      |     |        |         | 1: Enable boost       |

|      |     |        |         | Charge enable         |

| 3    | RW  | CH_EN  | 0b0     | 0: Disable charge     |

|      |     |        |         | 1: Enable charge      |

|      |     |        |         | EBL switch enable     |

| 2    | RW  | EBL_EN | 0b0     | 0: Close EBL          |

|      |     |        |         | 1: Open EBL           |

|      |     |        |         | EBR switch enable     |

| 1    | RW  | EBR_EN | 0b0     | 0: Close EBR          |

|      |     |        |         | 1: Open EBR           |

|      |     |        |         | Sleep mode enable     |

| 0    | RW  | SLP_EN | 0b0     | 0: Disable Sleep mode |

|      |     |        |         | 1: Enable Sleep mode  |

### 5.12.5 User configure Register 1

Address: 0b 00100

| Bits | R/W | fields     | default | Description                                  |

|------|-----|------------|---------|----------------------------------------------|

| 15:6 | R   | Reserved   | 0b0     | Must be kept at reset value.                 |

|      |     |            |         | LED current set                              |

|      |     |            |         | 00: 0.5 mA                                   |

| 5:4  | RW  | LED_DRV    | 0b10    | 01: 1 mA                                     |

|      |     |            |         | 10: 2 mA                                     |

|      |     |            |         | 11: 4 mA                                     |

|      |     |            |         | Boost maximum current threshold set          |

|      |     | BST_ITHSET | 0b10    | 00: Boost maximum current threshold 1.6A     |

| 3:2  | RW  |            |         | 01: Boost maximum current threshold 1.8A     |

|      |     |            |         | 10: Boost maximum current threshold 2.0A     |

|      |     |            |         | 11: Boost maximum current threshold 2.2A     |

|      |     |            |         | Earbud light load current set                |

|      |     |            |         | 00: Earbud light load current is set to 90%  |

| 1:0  | RW  | IOFF_SET   | 0b10    | 01: Earbud light load current is set to 95%  |

|      |     |            |         | 10: Earbud light load current is set to 100% |

|      |     |            |         | 11: Earbud light load current is set to 105% |

### 5.12.6 User configure Register 2

Address: 0b 00101

| Bits  | R/W | fields   | default | Description                  |

|-------|-----|----------|---------|------------------------------|

| 15:13 | R   | Reserved | 0b0     | Must be kept at reset value. |

| Bits  | R/W | fields      | default | Description                                        |

|-------|-----|-------------|---------|----------------------------------------------------|

|       |     |             |         | VSYS voltage set                                   |

|       |     |             |         | 000: Boost output voltage 4.8V                     |

|       |     |             |         | 001: Boost output voltage 4.85V                    |

|       |     |             |         | 010: Boost output voltage 4.9V                     |

| 12:10 | RW  | VSYS_SET    | 0b100   | 011: Boost output voltage 4.95V                    |

|       |     |             |         | 100: Boost output voltage 5V                       |

|       |     |             |         | 101: Boost output voltage 5.05V                    |

|       |     |             |         | 110: Boost output voltage 5.1V                     |

|       |     |             |         | 111: Boost output voltage 5.15V                    |

|       |     |             |         | VUSB current limit set                             |

|       |     |             |         | 00: VUSB current limit is set to 95%               |

| 9:8   | RW  | VUSB_CL_SET | 0b01    | 01: VUSB current limit is set to 100%              |

|       |     |             |         | 10: VUSB current limit is set to 105%              |

|       |     |             |         | 11: VUSB current limit is set to 110%              |

|       |     |             |         | Pre-charge current set                             |

|       |     |             |         | 00: Pre-charge current is set to 50%               |

| 7:6   | RW  | IPCH_SET    | 0b01    | 01: Pre-charge current is set to 100%              |

|       |     |             |         | 10: Pre-charge current is set to 150%              |

|       |     |             |         | 11: Pre-charge current is set to 150%              |

|       |     |             |         | Pre-charge terminate voltage set                   |

|       |     |             |         | 00: Pre-charge terminate voltage is 3.0V           |

| 5:4   | RW  | VPCHT_SET   | 0b01    | 01: Pre-charge terminate voltage is 3.1V           |

|       |     |             |         | 10: Pre-charge terminate voltage is 3.2V           |

|       |     |             |         | 11: Pre-charge terminate voltage is 3.3V           |

|       |     |             |         | Constant current charge current set                |

|       |     |             |         | 00: Constant current charge current is set to 100% |

| 3:2   | RW  | ICCCH_SET   | 0b0     | 01: Constant current charge current is set to 75%  |

|       |     |             |         | 10: Constant current charge current is set to 50%  |

|       |     |             |         | 11: Constant current charge current is set to 25%  |

|       |     |             |         | Re-charge threshold voltage set                    |

|       |     |             |         | 00: Re-charge threshold voltage is 3.9V            |

| 1:0   | RW  | VRCHT_SET   | 0b01    | 01: Re-charge threshold voltage is 4.0V            |

|       |     |             |         | 10: Re-charge threshold voltage is 4.1V            |

|       |     |             |         | 11: Re-charge threshold voltage is 4.2V            |

# 5.12.7 User configure Register 3

Address: 0b 00110

| Bits | R/W | fields        | default | Description                            |

|------|-----|---------------|---------|----------------------------------------|

| 15:7 | R   | Reserved      | 0b0     | Must be kept at reset value.           |

| 6:5  | RW  | EBLR_ILIM_SET | 0b01    | EBL/EBR limit current set<br>00: 150mA |

| Bits | R/W | fields     | default | Description                                             |

|------|-----|------------|---------|---------------------------------------------------------|

|      |     |            |         | 01: 250mA                                               |

|      |     |            |         | 10: 350mA                                               |

|      |     |            |         | 11: 450mA                                               |

|      |     |            |         | Constant current charge terminate voltage set           |

|      |     |            |         | 000: Constant current charge terminate voltage is 4.2V  |

|      |     |            |         | 001: Constant current charge terminate voltage is 4.1V  |

|      |     |            |         | 010: Constant current charge terminate voltage is 4.3V  |

| 4:2  | RW  | VCCCHT_SET | 0b0     | 011: Constant current charge terminate voltage is 4.35V |

|      |     |            |         | 100: Constant current charge terminate voltage is 4.4V  |

|      |     |            |         | 101: Constant current charge terminate voltage is 4.2V  |

|      |     |            |         | 110: Constant current charge terminate voltage is 4.2V  |

|      |     |            |         | 111: Constant current charge terminate voltage is 4.2V  |

|      |     |            |         | Charge terminate current set                            |

|      |     |            |         | 00: Charge terminate current minus 10mA                 |

| 1:0  | RW  | ICHT_SET   |         | 01: Charge terminate current minus 5mA                  |

|      |     |            |         | 10: Charge terminate current no change                  |

|      |     |            |         | 11: Charge terminate current plus 5mA                   |

### 5.12.8 Watchdog Register

Address: 0b 01011

| Bits  | R/W | Fields   | default | Description                                |

|-------|-----|----------|---------|--------------------------------------------|

| 15:10 | R   | Reserved | 0b0     | Must be kept at reset value.               |

|       |     | WDG_DATA | 0x1ff   | Watchdog counter set                       |

| 9:1   | RW  |          |         | Only set watchdog counter when WDG_EN is 0 |

|       | RW  | WDG_EN   | 0b0     | Watchdog enable                            |

| 0     |     |          |         | 0: Disable watchdog                        |

|       |     |          |         | 1: Enable watchdog                         |

### 5.12.9 COML/R Register

Address: 0b 01100

| Bits | R/W | fields       | default | Description                  |

|------|-----|--------------|---------|------------------------------|

| 15   | R   | Reserved     | 0b0     | Must be kept at reset value. |

|      |     |              |         | EBL pin input enable         |

| 14   | RW  | COML_EBL_IEN | 0b0     | 0: Disable EBL pin input     |

|      |     |              |         | 1: Enable EBL pin input      |

|      |     |              |         | EBR pin input enable         |

| 13   | RW  | COMR_EBR_IEN | 0b0     | 0: Disable EBR pin input     |

|      |     |              |         | 1: Enable EBR pin input      |

| 12   | RW  | COML_IEN     | 0b0     | COML pin input enable        |

|      |     |              |         | 0: Disable COML pin input    |

| Bits | R/W | fields       | default | Description                                    |

|------|-----|--------------|---------|------------------------------------------------|

|      |     |              |         | 1: Enable COML pin input                       |

|      |     |              |         | COMR pin input enable                          |

| 11   | RW  | COMR_IEN     | 0b0     | 0: Disable COMR pin input                      |

|      |     |              |         | 1: Enable COMR pin input                       |

|      |     |              |         | EBL pin output enable                          |

| 10   | RW  | COML_EBL_OEN | 0b0     | 0: Disable EBL pin output                      |

|      |     |              |         | 1: Enable EBL pin output                       |

|      |     |              |         | EBR pin output enable                          |

| 9    | RW  | COMR_EBR_OEN | 0b0     | 0: Disable EBR pin output                      |

|      |     |              |         | 1: Enable EBR pin output                       |

|      |     |              |         | Communication enable mode 2 I2C control        |

| 8    | RW  | COM_MD2EN    | 0b0     | 0: Disable mode 2                              |

|      |     |              |         | 1: Enable mode 2                               |

|      |     |              |         | Communication enable mode 1 COML/R pin control |

| 7    | RW  | COM_MD1EN    | 0b0     | 0: Disable mode 1                              |

|      |     |              |         | 1: Enable mode 1                               |

|      |     |              |         | COML pin output enable                         |

| 6    | RW  | COML_OEN     | 0b0     | 0: Disable COML pin output                     |

|      |     |              |         | 1: Enable COML pin output                      |

|      |     |              |         | COMR pin output enable                         |

| 5    | RW  | COMR_OEN     | 0b0     | 0: Disable COMR pin output                     |

|      |     |              |         | 1: Enable COMR pin output                      |

|      |     |              |         | Communication selection                        |

| 4    | RW  | COM_I2C_SEL  | 0b0     | 0: COML/R pin control                          |

|      |     |              |         | 1: I2C control                                 |

|      |     |              |         | COML pin input signal                          |

| 3    | R   | COML_IN      | 0b0     | 0: COML pin input low                          |

|      |     |              |         | 1: COML pin input high                         |

|      |     |              |         | COMR pin input signal                          |

| 2    | R   | COMR_IN      | 0b0     | 0: COMR pin input low                          |

|      |     |              |         | 1: COMR pin input high                         |

|      |     |              |         | COML pin output signal                         |

| 1    | RW  | COML_O       | 0b0     | 0: COML pin output low                         |

|      |     |              |         | 1: COML pin output high                        |

|      |     |              |         | COMR pin output signal                         |

| 0    | RW  | COMR_O       | 0b0     | 0: COMR pin output low                         |

|      |     |              |         | 1: COMR pin output high                        |

### 5.12.10 LED Register

Address: 0b 01101

| Bits  | R/W | fields       | default | Description                  |

|-------|-----|--------------|---------|------------------------------|

| 15:14 | R   | Reserved     | 0b0     | Must be kept at reset value. |

|       |     |              |         | LED4 Status                  |

| 13    | RW  | LED4_I2C_ST  | 0b0     | 0: Off                       |

|       |     |              |         | 1: On                        |

|       |     |              |         | LED3 Status                  |

| 12    | RW  | LED3_I2C_ST  | 0b0     | 0: Off                       |

|       |     |              |         | 1: On                        |

|       |     |              |         | LED2 Status                  |

| 11    | RW  | LED2_I2C_ST  | 0b0     | 0: Off                       |

|       |     |              |         | 1: On                        |

|       |     |              |         | LED1 Status                  |

| 10    | RW  | LED1_I2C_ST  | 0b0     | 0: Off                       |

|       |     |              |         | 1: On                        |

| 9:3   | R   | Reserved     | 0b0     | Must be kept at reset value. |

|       |     |              |         | LED mode status              |

|       |     |              |         | 00: 2 LED mode               |

| 2:1   | RW  | LED_I2C_MDST | 0b0     | 01: 3 LED mode               |

|       |     |              |         | 10: 1 LED mode               |

|       |     |              |         | 11: 4 LED mode               |

|       |     |              |         | LED I2C control enable       |

| 0     | RW  | LED_I2C_EN   | 0b0     | 0: LED Hardware control      |

|       |     |              |         | 1: LED I2C control           |

### 5.12.11 ADC Register

Address: 0b 01110

| Bits | R/W | fields    | default | Description                  |

|------|-----|-----------|---------|------------------------------|

| 15:4 | R   | ADC_DATA  | 0b0     | ADC measure 12 bit data.     |

|      |     |           |         | ADC channel select           |

|      |     |           |         | 000: Channel VBAT            |

|      |     |           |         | 001: Channel VRCH            |

|      |     |           |         | 010: Channel VSENS_EBL       |

| 3:1  | RW  | ADC_CHSEL | 0b0     | 011: Channel VSENS_EBR       |

|      |     |           |         | 100: Channel VCOM            |

|      |     |           |         | 101: Channel VIC             |

|      |     |           |         | 110: Channel VIR             |

|      |     |           |         | 111: Channel AVSS            |

| 0    | R   | Reserved  | 0b0     | Must be kept at reset value. |

# 5.12.12 DEBUG Register

Address: 0b 01111

| Bits  | R/W   | fields    | default | Description                                                   |

|-------|-------|-----------|---------|---------------------------------------------------------------|

|       |       |           |         | I2C/COML/COMR PAD filter enable.                              |

| 15    | RW    | FIL_EN    | 0b1     | 0: Filter is disabled                                         |

|       |       |           |         | 1: Filter is enabled                                          |

| 14:12 | R     | Reserved  | 0b0     | Must be kept at reset value.                                  |

|       |       |           |         | Charge status timeout time select                             |

|       |       | CH_TO_SEL | 0b0     | 00: 120 minute                                                |

| 11:10 | R/W   |           |         | 01: 180 minute                                                |

|       |       |           |         | 10: 240 minute                                                |

|       |       |           |         | 11: 60 minute                                                 |

|       |       |           |         | Battery is charged fully, set by software. It will affect the |

|       |       | VBAT_FULL | 0b0     | LED display                                                   |

|       | D 44/ |           |         | 0: Battery is not charged fully. LED displays normally        |

| 9     | R/W   |           |         | according to battery power                                    |

|       |       |           |         | 1: Battery is charged fully. LED displays according to        |

|       |       |           |         | battery full charge                                           |

| 8:0   | R     | Reserved  | 0b0     | Must be kept at reset value.                                  |

#### 6 Electrical characteristics

#### 6.1 Absolute maximum ratings

The maximum ratings are the limits to which the device can be subjected without permanently damaging the device. Note that the device is not guaranteed to operate properly at the maximum ratings. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

Table 6-1 Absolute maximum ratings

| Symbol            | Parameter                                       | Min  | Max | Unit |

|-------------------|-------------------------------------------------|------|-----|------|

| V <sub>BUS</sub>  | Power supply pin from USB other 5V input        | -0.3 | 20  | V    |

| V <sub>BAT</sub>  | Battery voltage                                 | -0.3 | 7   | V    |

| V <sub>SYS</sub>  | Output Voltage                                  | -0.3 | 7   | V    |

| Vcc               | LDO output voltage and Internal logic voltage   | -0.3 | 7   | V    |

| V <sub>IO</sub>   | I/O pin voltage (LEDx, ISET, EN, NTC, SCL, SDA) | -0.3 | 7   | V    |

| V <sub>EBLR</sub> | Earbuds positive terminal voltage (EBL/EBR)     | -0.3 | 7   | V    |

| Vsw               | Switching node voltage (SW)                     | -0.3 | 7   | V    |

|                   | Thermal characteristics                         |      |     |      |

| TJ                | Operating junction temperature                  | -40  | 150 | °C   |

| T <sub>stg</sub>  | Storage temperature                             | -65  | 150 | °C   |

### 6.2 Recommended operation conditions

**Table 6-2 Recommended operation conditions**

| Symbol           | Parameter                                     | Min | Тур | Max  | Unit |

|------------------|-----------------------------------------------|-----|-----|------|------|

| Vusa             | Power supply pin from USB other 5V input      | 4.4 | 5.0 | 5.5  | V    |

| V <sub>BAT</sub> | Battery voltage                               | 2.2 | 4.0 | 4.4  | V    |

| Vsys             | BOOST output Voltage                          | 4.8 | 5.0 | 5.15 | V    |

| Vcc              | LDO output voltage and Internal logic voltage | 2.0 | 3.3 | 3.6  | V    |

|                  | Thermal characteristics                       |     |     |      |      |

| T <sub>A</sub>   | Operating ambient temperature                 | -20 | _   | 85   | °C   |

#### 6.3 Electrical sensitivity

The device is strained in order to determine its performance in terms of electrical sensitivity. Electrostatic discharges (ESD) are applied directly to the pins of the sample.

**Table 6-3 Electrostatic Discharge characteristics**

| Symbol    | Parameter                     | Conditions              | Value | Unit |

|-----------|-------------------------------|-------------------------|-------|------|

| \/        | Electrostatic discharge       | T <sub>A</sub> = 25 °C; | 13000 | \/   |

| Vesd(HBM) | voltage (human body model)    | JS-001-2017             | ±2000 | V    |

| \/        | Electrostatic discharge       | T <sub>A</sub> = 25 °C; | .1000 | \/   |

| Vesd(cdm) | voltage (charge device model) | JS-002-2018             | ±1000 | V    |

### 6.4 Power supplies voltages and currents

Table 6-4 Power supplies voltages and currents

| Symbol | Parameter                    | Conditions                                                         | Min | Тур | Max | Unit |

|--------|------------------------------|--------------------------------------------------------------------|-----|-----|-----|------|

| lα     | Sleep mode quiescent current | V <sub>BAT</sub> = 5 V, T <sub>A</sub> = 25 °C                     |     |     | 5.0 | μΑ   |

| ton    | Turn-on time                 | V <sub>USB</sub> > V <sub>UVLO</sub> to outputs ready              | 5.0 |     | I   | ms   |

| Vcc    | VCC regulator voltage        | $I_{VCC} = 0 \text{ to } 50 \text{ mA } (V_{BAT} > 3.4 \text{ V})$ | 3.1 | 3.3 | 3.5 | V    |

### 6.5 Logic input characteristics

Table 6-5 Logic input characteristics

| Symbol           | Parameter                | Conditions | Min                    | Тур | Max        | Unit |

|------------------|--------------------------|------------|------------------------|-----|------------|------|

| VIL              | Input logic low voltage  | _          | 0                      | _   | 0.35 * Vcc | ٧    |

| V <sub>IH</sub>  | Input logic high voltage | _          | 0.65 * V <sub>CC</sub> | _   | 5.5        | V    |

| V <sub>HYS</sub> | Input logic hysteresis   | _          | 100                    | 1   |            | mV   |

### 6.6 Open drain outputs characteristics

Open drain output pins include SCL, SDA, IRQ.

Table 6-6 Open drain output characteristics

| Symbol | Parameter                     | Conditions            | Min | Тур | Max | Unit |

|--------|-------------------------------|-----------------------|-----|-----|-----|------|

| Vol    | Output logic low voltage      | I <sub>O</sub> = 5 mA | _   | _   | 0.1 | V    |

| loz    | Output high impedance leakage | Vo = Vbat             | -2  | _   | 2   | μA   |

#### 6.7 NTC characteristics

**Table 6-7 NTC characteristics**

| Symbol              | Parameter                          | Conditions | Min | Тур                    | Max | Unit |

|---------------------|------------------------------------|------------|-----|------------------------|-----|------|

| V <sub>TL</sub>     | Low Temperature threshold voltage  |            | _   | 0.6 * V <sub>SYS</sub> | _   | V    |

| V <sub>TH</sub>     | High Temperature threshold voltage | _          | _   | 0.3 * V <sub>SYS</sub> | _   | V    |

| V <sub>offset</sub> | Offset Volatage                    | _          | _   | _                      | 5   | mV   |

### 6.8 Switching charger characteristics

**Table 6-8 Charger characteristics**

| Symbol              | Parameter                          | Conditions                      | Min       | Тур | Max | Unit |

|---------------------|------------------------------------|---------------------------------|-----------|-----|-----|------|

| V <sub>CVCH</sub>   | CV Charge voltage                  | Programmable                    | 4.1       | 4.2 | 4.4 | V    |

| V CVCH              | CV Charge voltage precision        | _                               | _         | 0.5 | _   | %    |

| Ісссн               | CC Charge current                  | $R_{CCCH} = 20 \text{ K}\Omega$ | _         | 0.5 | _   | Α    |

| I <sub>PCH</sub>    | Pre-Charge current                 | R <sub>CCCH</sub> = 20 KΩ       | 40        | 50  | 60  | mA   |

| I <sub>TER</sub>    | Charge terminate current           | _                               | Ірсн + 10 |     |     | mA   |

| V <sub>PCH</sub>    | Pre-Charge to CC charge transition | Programmable                    | _         | 3.0 | _   | V    |

| V <sub>PCHHYS</sub> | Pre-Charge hysteresis voltage      | _                               | _         | 200 | _   | mV   |

| V <sub>RCH</sub>    | Re-Charge threshold                | _                               | _         | 4   | _   | V    |

| V <sub>RCHHYS</sub> | Re-Charge hysteresis voltage       |                                 | _         | 200 | _   | mV   |

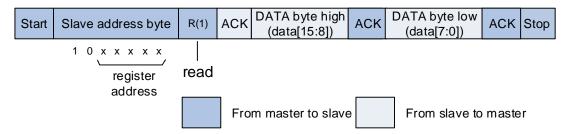

Figure 6-1 Constant current charging efficiency

Temperture(°C)

Charge Time (S)  $Icc = 500mA, Ta = 25^{\circ}C$

Figure 6-2 Constant current charging chip case temperature

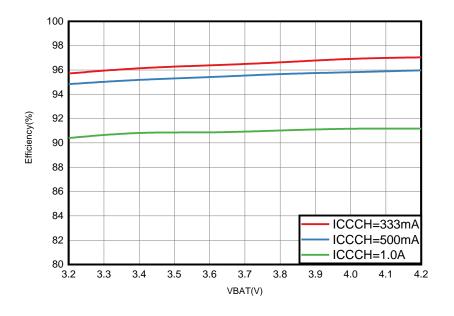

#### 6.9 Boost converter characteristics

**Table 6-9 Boost converter characteristics**

| Symbol              | Parameter                         | Conditions                                       | Min  | Тур  | Max  | Unit |

|---------------------|-----------------------------------|--------------------------------------------------|------|------|------|------|